三星正研发CMM-H混合存储模组:通过CXL技术同时连接DRAM内存和NAND闪存

时间:2024-03-21

来源:未知

作者:Gushan

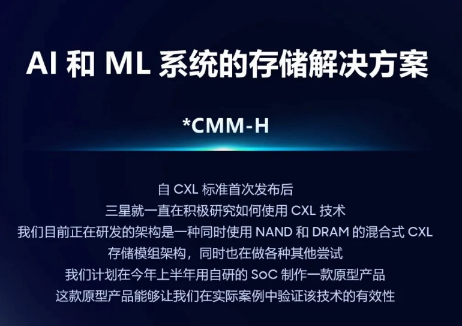

三星半导体在其微信公众号发布的2024年中国闪存市场峰会上透露,目前正在进行CMM-H混合存储CXL模组的研发工作。这款模组整合了DRAM内存与NAND闪存技术,并利用新一代高速互联标准CXL(Compute Express Link)来提供显著提升的数据吞吐性能和更低的传输延迟,从而在CPU与外部设备间构建高效的数据交换桥梁。

根据展示的图示信息,CMM-H模组能够通过CXL接口直接实现在闪存部分与CPU之间的块I/O传输,同时也能通过DRAM缓存及CXL界面进行64字节粒度的内存I/O传输操作。

该模组具备细粒度访问能力,有助于降低总体拥有成本(TCO),并有可能成为持久内存解决方案的一个选项。按照三星公布的计划,在2023年上半年将制作一款基于FPGA控制、支持CXL 1.1规范的CMM-H原型产品,采用E3.L 2T规格设计,最大容量可达4TB,峰值带宽为8GB/s。

针对未来商用量产阶段的CMM-H模组,三星预计将于2026年推出基于ASIC成熟控制器的版本,届时将支持CXL 3.0规范,最大容量可扩展至16TB,最大带宽提升到64GB/s。

另外,在CXL-D纯内存模组领域,三星规划于明年第一季度推出第二代128GB容量的产品样品,采用1b纳米制程工艺的DRAM颗粒,运行速度高达6400MT/s。接下来,三星还将在2024年进一步丰富其第二代CXL-D模组产品线,相继推出512GB和256GB两种不同容量的产品。